Semicap. Обзор технологий высокоплотного монтажа

От пластиковых корпусов к современным

технологиям: стратегическое значение технологий высокоплотного монтажа

полупроводников

Для удобства статья разделена на две части, первая из которых – обзор процессов производства, а вторая – обзор специализированных компаний Teradyne, Formfactor, Advantest и Camtek. Возможно, со временем появятся отдельная статья по Keysight и другим компаниям, но приведенный в статье материал ещё неоднократно нам понадобиться. Мне бы хотелось, чтобы статья была написана раньше, поскольку приведенная в ней информации будет полезной при изучении отрасли производства полупроводниковой продукции.

Плюсы технологий высокоплотного монтажа

Ещё не так давно высокоплотный монтаж был далеко не самой важной задачей в процессе производства полупроводников – дело ограничивалось тем, что при помощи ряда манипуляций кусок кремния становился «волшебным», который каким-то образом монтировался на плату и о нём благополучно забывали. Но с момента открытия закона Мура (Moore’s law) инженеры осознали, что при помощи технологий высокоплотного монтажа они могут улучшить характеристики продукции, т.к. его применение обеспечивает лучшую проводимость, а решение вопросов ввода/вывода (input/output) по-прежнему остаётся одной из главных задач при производстве полупроводников.

Удивительно, но в прошлом ни одна из компаний, специализирующиеся на технологиях высокоплотного монтажа, не считались столь же важными, как компании, обеспечивающие традиционные процессы производства. При производстве полупроводников технологии высокоплотного монтажа рассматривался в качестве второстепенного игрока, как это бывает, к примеру, в банковской сфере с её разделением на клиентский офис и офис поддержки. Но в связи с увеличением сложности современных полупроводников возникла совершенно новая область производства, в которой особое внимание уделяется технологиям высокоплотного монтажа. В статье мы ознакомимся с производственными процессами, и поймем, чем различается монтаж по технологиям 2,5D или 3D.

Краткая история технологий высокоплотного монтажа

Безусловно, существует множество различных технологий высокоплотного монтажа, но мы рассмотрим самые простые, а затем перейдем к наиболее современным.

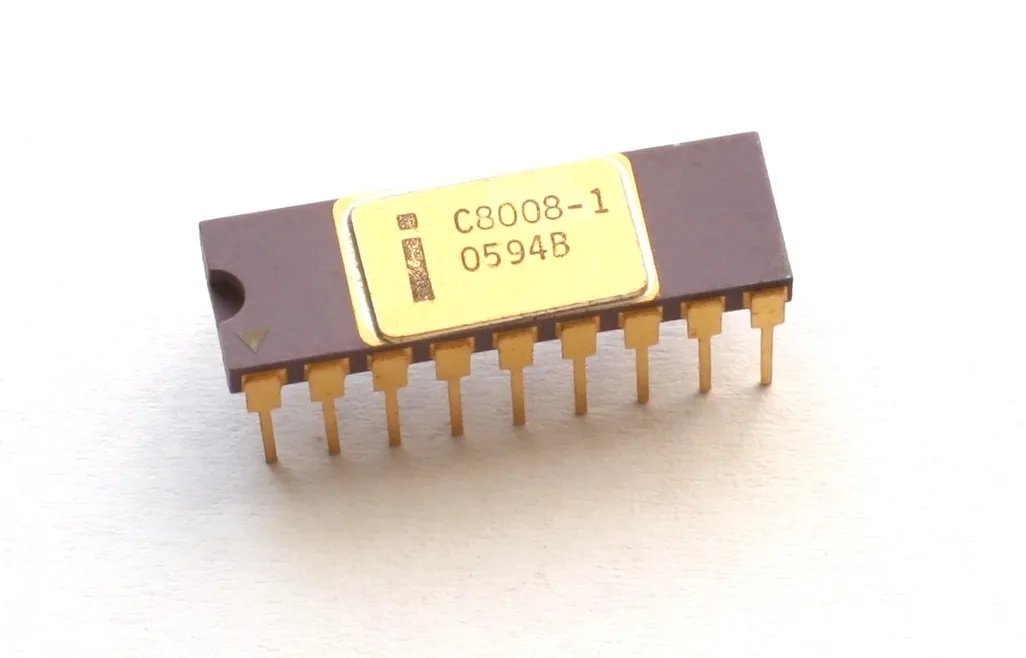

Монтаж по технологии DIP (1964 – 1980)

Монтаж с использованием пластиковой упаковки получил широкое распространение в 70-х годах прошлого века и применялся вплоть до появления более современных технологий монтажа. При использовании этой технологии полупроводники упаковывались в пластиковые корпуса, содержащие два параллельных ряда выступающих электрических контактов (выводные рамки) при помощи которых осуществлялся монтаж на печатную плату (printed circuit board, PCB).

Ниже приведено фото Intel 8008 – фактически одного из первых образцов современных микропроцессоров, культовая технология монтажа которого запомнилась надолго. Так что если вы когда-нибудь столкнетесь с забавными фотографиями полупроводников, которые выглядят как маленькие паучки, то это будут полупроводники, смонтированные по технологии DIP.

Хотя существуют и другие разновидности монтажа типа DIP, перейдем к следующей парадигме технологии монтажа, зародившейся в 1980-х годах – поверхностному монтажу (surface-mount technology, SMT).

Поверхностный монтаж (1980 – 1990-е годы)

Раньше процесс поверхностного монтажа выполнялся вручную, но теперь он в значительной степени автоматизирован, что создало целый ряд проблем, таких как попкорнинг (popcorning) – это когда в окпроцессе пайки нагревается влага внутри полупроводника, что вызывает проблемы в печатной плате из-за быстрого нагрева и охлаждения. Следует отметить, что с каждым новым этапом эволюции процесса поверхностного монтажа возрастает сложность и количество отказов.

Монтаж при помощи шариковых массивов (1990-е –

2000-е годы)

По мере роста требований к скорости полупроводников растет и потребность в современных методах монтажа. В то время как процесс Quad-Flat No-leads, QFN и другие технологии поверхностного монтажа, безусловно, находят применение в производстве электроники, хочется обратить внимание на новые поколения технологий монтажа, одним из которых является процесс монтажа при помощи шариковых массивов – Ball Grid Array, BGA.

На текущий момент технология BGA – основной способ соединения элементов друг с другом.

Современные технологии монтажа (2000 – 2010-е годы)

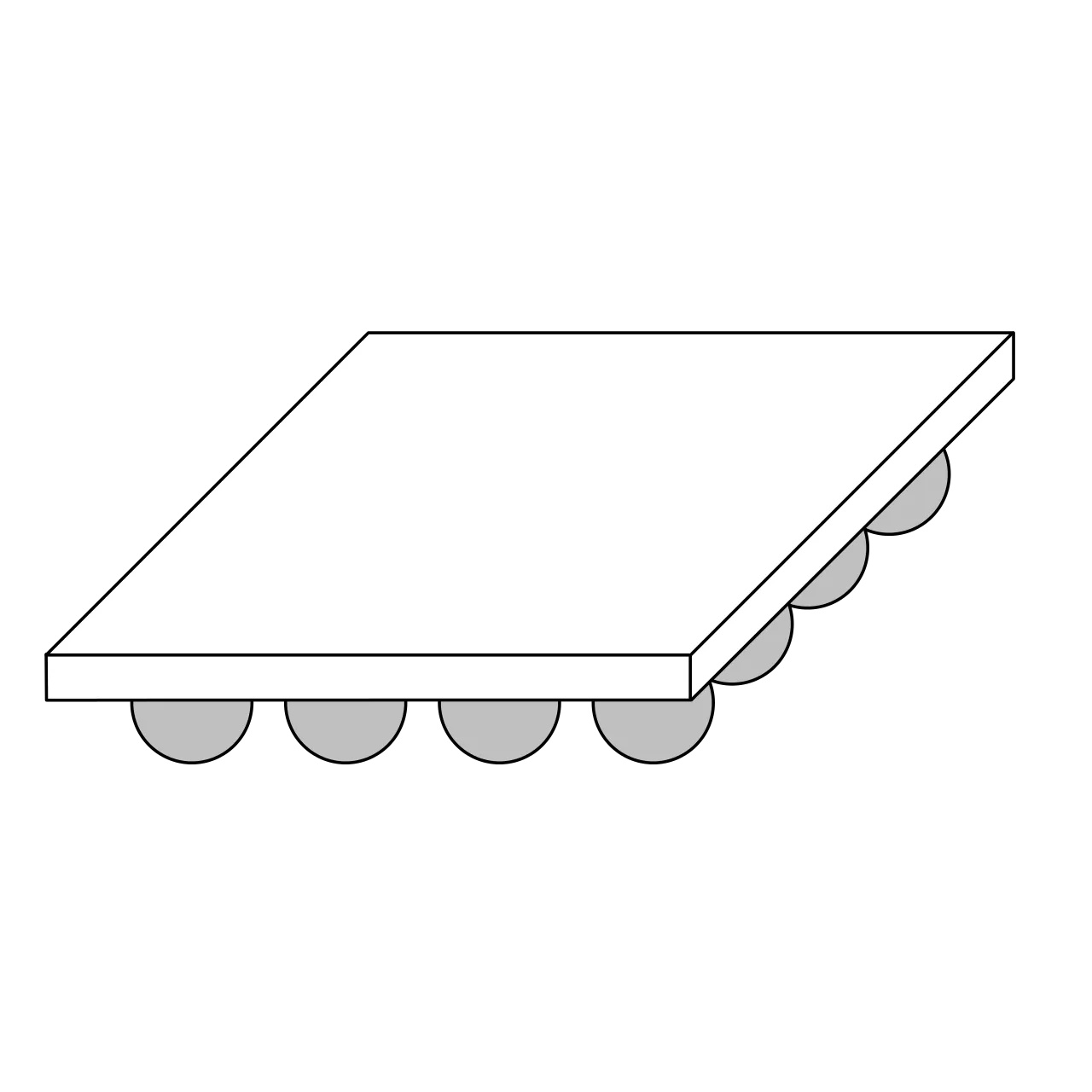

Перевернутый чип (Flip chip)

Один из самых распространенных методов монтажа – технология монтажа flip chip была изобретена компанией IBM, и часто его сокращенно называют C4. В случае с технологией flip chip это не отдельный форм-фактор корпусирования модуля, а скорее стиль упаковки – в чипе не используются межчиповые соединения – чип переворачивается лицом к другому чипу соединительной подложкой между ними – отсюда и название «flip chip» (перевернутый чип).

Общая схема создания интегральных схем:

1. На поверхность микросхем наносится специализированное напыление

2. На каждую из площадок наносится точка припоя

3. Чипы разрезаются

4. Микросхемы переворачиваются и располагаются так, чтобы точки припоя были направлены в сторону схемы

6. Установленная микросхема заполнена электроизолирующим клеем

Проволочное соединение (Wirebond)

Обратите внимание на различия технологий flip chip от wirebond (проволочные соединения). Помните монтаж по технологии DIP, упомянутый ранее? В общем и целом – это проволочное соединение, когда матрица использует провода для соединения элементов друг с другом, которое затем припаивается к печатной плате. Проволочное соединение, таким образом, это не конкретная технология, а скорее набор ранее используемых технологий, который охватывает множество различных типов монтажа и корпусирования. Технологию проволочного соединения правильнее всего сравнивать с технологий flip chip, предшественницей которой она, по сути дела, и является.

Новейшие технологии монтажа (с конца нулевых по настоящее

время)

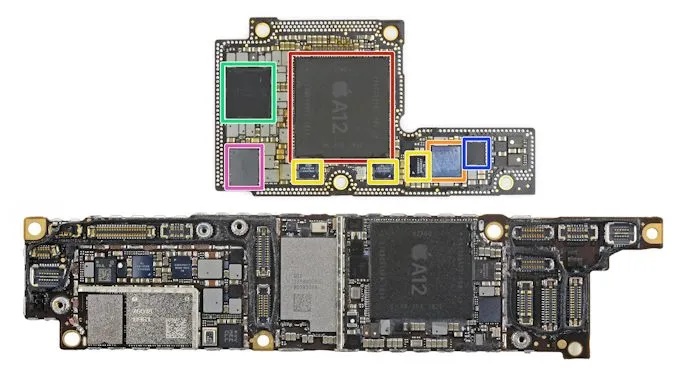

Мы все медленнее входим в новейшую эру полупроводников, и хотелось бы затронуть некоторые концепции более высокого уровня. На самом деле существуют различные уровни монтажа, которые вписываются в общий процесс. Большинство технологий монтажа, о которых упоминалось ранее, были сосредоточены на монтаже чипов на печатные платы, но наиболее важное направление использования новейших технологий монтажа – мобильные устройства.

Мобильные устройства во многих отношениях является главным объектом применения новейших технологий монтажа. Телефон, например, это огромное количество кремния в минимально возможном пространстве, гораздо более плотном, чем ноутбук или компьютер. При этом все элементы должны иметь пассивное охлаждение и, конечно, быть как можно тоньше. Каждый год компании Apple и Samsung анонсировали более быстрый, но, что более важно, более тонкий телефон, и это подталкивало производителей к разработке новых технологий монтажа. Многие из концепций, которые обсуждаются в этой статье, зародились в результате исследований технологий для мобильных устройств и теперь распространились на всю остальную полупроводниковую промышленность.

Корпусирование

интегрированных чипов

Технология корпусирования интегрированных чипов (Chip Scale Packaging) может выполнятся в разных вариантах, и изначально означает технологию монтажа чипов в корпус, размер которого не сильно превышает размер матрицы чипа. При этом чип, помещаемый в корпус, должен быть одноматричным и легко монтируемым. Монтаж по технологии CSP получил развитие благодаря применению при производстве смартфонов.

В середине двухтысячных монтаж по технологии CSP стал стандартом де-факто, что позволяло максимально экономить площадь монтажа. Существует множество различных вариантов технологии CSP: flip chip, специализированная подложка и другие технологии – все они входят в эту классификацию.

Корпусирование

пластин

Помимо корпусирования интегральных схем по технологии CSP существует вариант корпусирования интегральных схем на уровне пластин (Wafer-level packaging) при котором чип крепится на кремниевой матрице. В этом случае корпус представляет собой сложную в производстве компактную кремниевую матрицу с высокоплотными каналами ввода-вывода. В настоящее время происходит настоящая революция в области корпусирования интегральных схем по технологии CSP, но будущее за корпусированием интегральных схем на уровне пластин.

В результате эволюции, технологии корпусирования поменялись местами с интегрированными схемами, и наоборот. Производство интегрированных схем по таким технологиям очень дорого, особенно по сравнению с технологиями монтажа предыдущих поколений – так зачем же тогда огромные инвестиции вкладываются в развитие новых технологий?

Технологии

будущего

С моей точки зрения основной вектор развития технологий лежит в области гетерогенных вычислений (heterogeneous computing), при реализации которых особое значение имеет сопряжение модулей между собой – собственно говоря, именно поэтому на первое место выходят новейшие технологии монтажа и корпусирования.

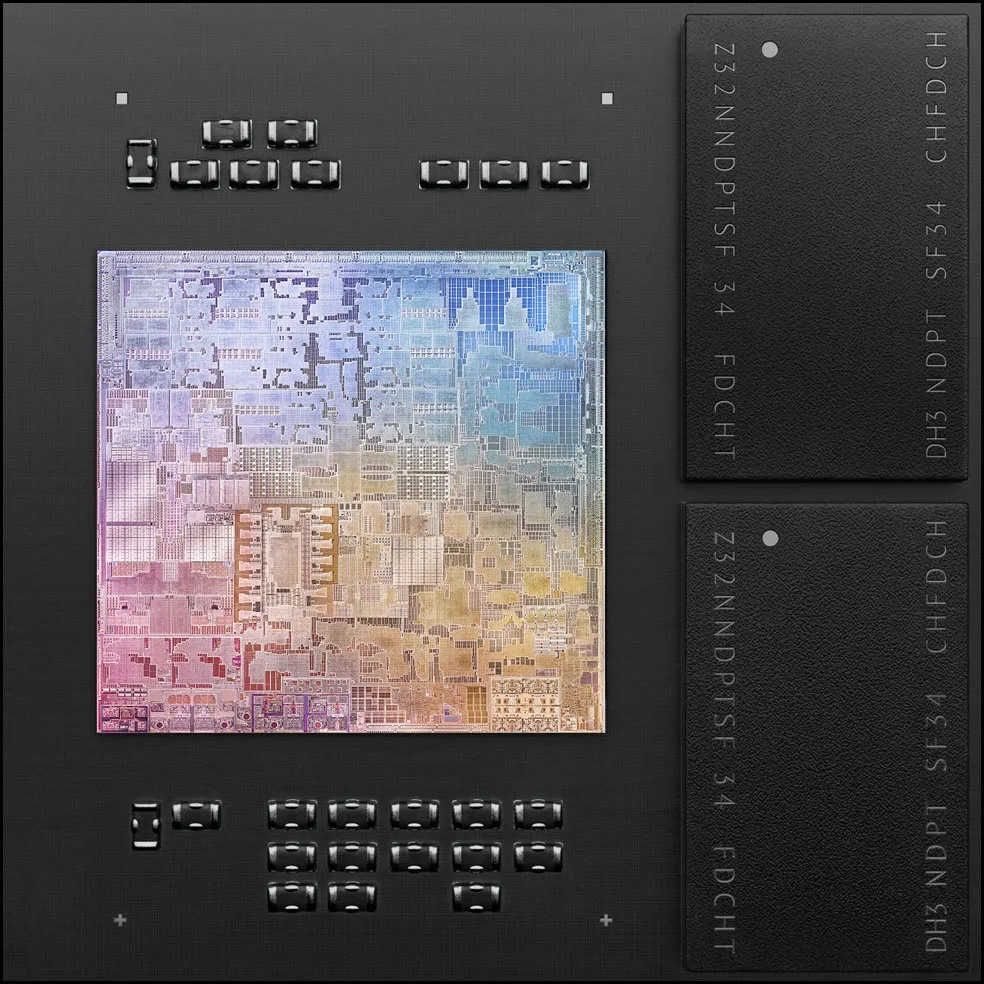

Давайте рассмотрим M1 – классическую конфигурацию гетерогенных вычислений с унифицированной памятью «на борту». Для меня M1 – это просто «ещё одна технология», а водораздел между «старыми» и «новыми» технологиями. M1 – это будущее технологий, и вскоре многие последуют примеру Apple. Обратите внимание, что «система на чипе» (system on chip) не является гетерогенной, но принцип, который приближает память к SOC, является таковым.

Вот цитата из их технического описания.

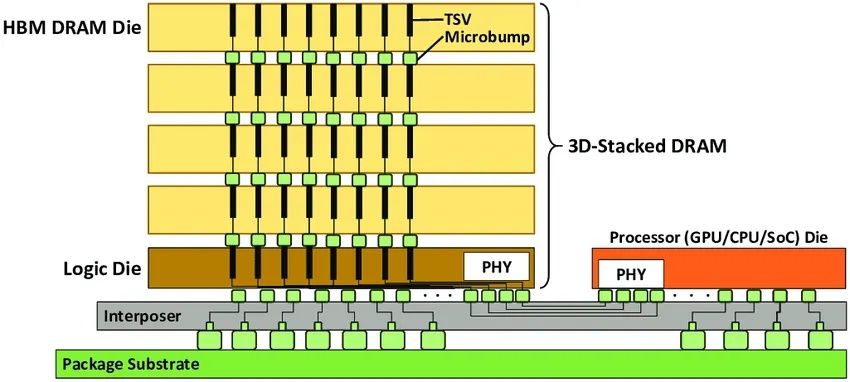

Вместо использования многочисленных дискретных чипов памяти, окружающих графический процессор, как это принято в традиционных конструкциях плат для графических процессоров с GDDR5, HBM2 включает один или несколько вертикальных стеков из нескольких плашек памяти. Плашки памяти связаны между собой практически невидимыми проводами, которые создаются с помощью сквозных кремниевых отверстий и микровыступов. Одна матрица HBM2 емкостью 8 Гб содержит более 5 000 сквозных отверстий. Затем для соединения стеков памяти и GPU используется пассивный кремниевый интерфейс (interposer). Общая сборка стека HBM2, матрицы GPU и кремниевого интерфейса упакована в корпус BGA размером 55 мм x 55 мм.

Отсюда следует вывод: технологии производства полупроводников не стоят на месте и постоянно совершенствуются. Давайте поподробнее рассмотрим приведенные выше технологии, и начнём обзор с двух основных категорий корпусирования – 2,5D и 3D.

Технология

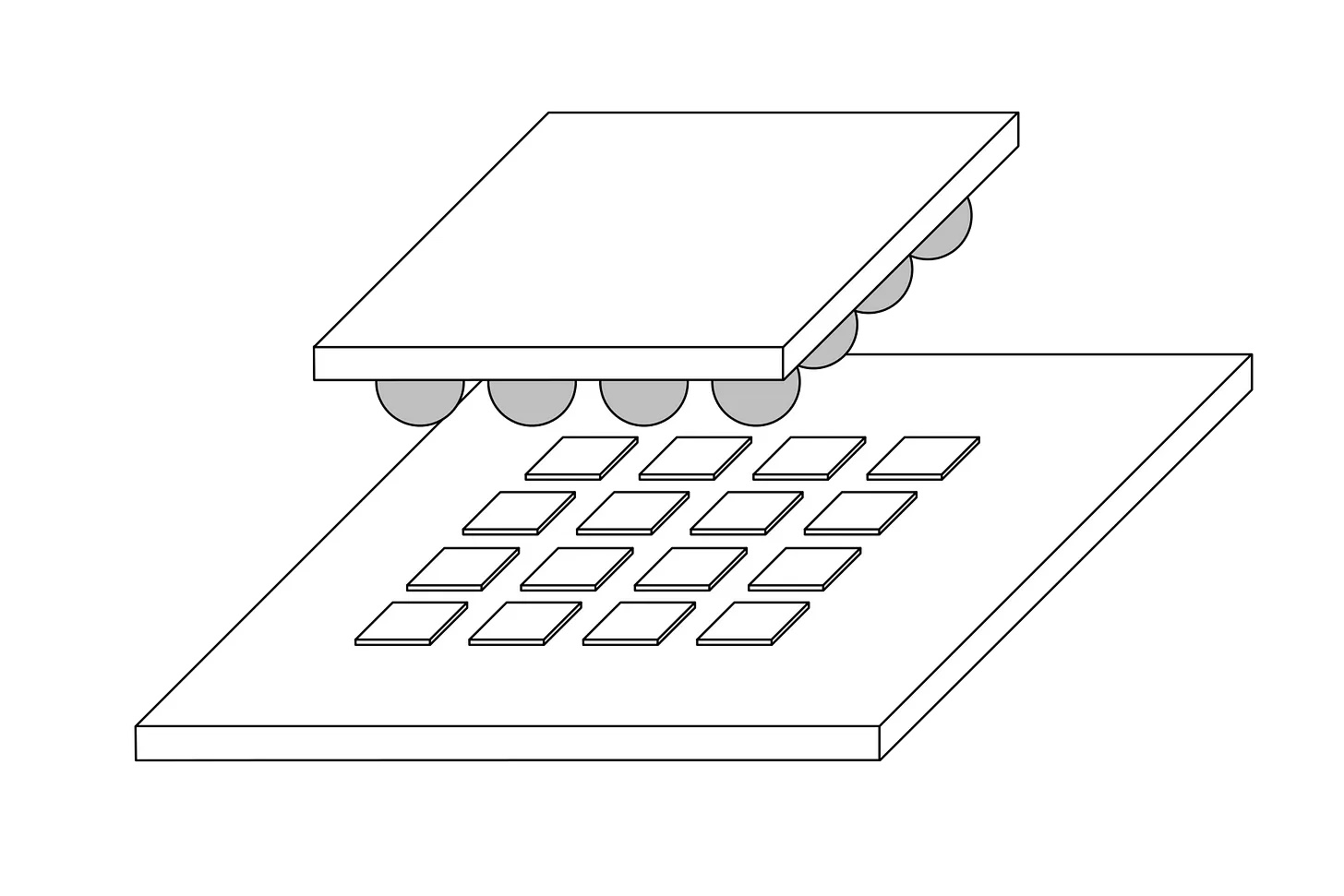

монтажа 2.5D

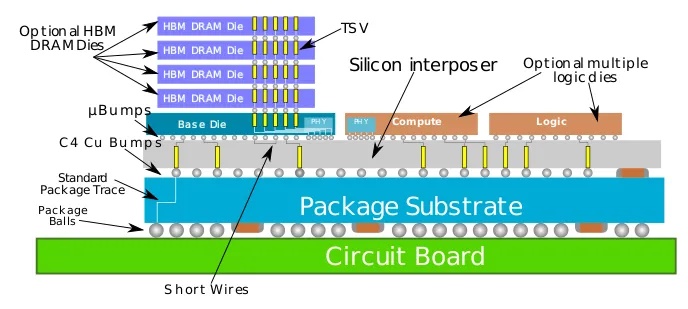

Технология монтажа 2,5D представляет собой эволюцию технологии flip chip, о которой говорилось выше, но вместо монтажа одной матрицы на печатную плату, матрицы монтируются поверх одного кремниевого интерфейса (общая схема монтажа приведена ниже).

Технология монтажа 2,5D – это как дверь в подвал дома вашего соседа, которая представляет собой канавку, либо сквозное отверстие в кремниевой пластине (Through Silicon Vias, TSV), посредством которой происходит «соединение» с соседним домом. Такой вариант монтажа работает медленнее, чем в случае унифицированного монтажа элементов на кремниевой пластине, но поскольку чистая производительность определяется общей производительностью сборки, то уменьшение расстояния и увеличение взаимосвязи между элементами перевешивают имеющиеся недостатки. Преимуществом данного вида монтажа является то, что производители имеют возможность использовать проверенные конфигурации элементов для быстрой сборки более крупных и сложных пакетов. С точки зрения производительности лучше, если бы сборка пакета производилась на одной пластине, но подобный процесс значительно упрощает производство, особенно при небольших размерах.

Отдельные элементы сборки часто называют «чиплетами» (chiplets), на основе которых можно собрать пакет с необходимым функционалом.

Чиплеты и монтаж по технологии 2,5D будут в ходу ещё долгое время – это настоящие рабочие лошадки, которые позволяют быстро и дёшево реализовывать необходимый функционал. Кроме того, технология 2,D хорошо масштабируется и может быть повторно использована с новыми чиплетами, что позволяет создавать новые чипы в том же формате корпуса путём замены чиплетов. Новые варианты реализации Zen3 являются примером увеличения производительности чиплетов, однако такой вариант монтажа не дотягивает по производительности до технологии 3D.

Технология монтажа 3D

Примером сегмента рынка полупроводников, целиком перешедшего на технологию монтажа 3D, является производство модулей памяти. Переход производства памяти на технологию монтажа даёт представление о векторе развития всей полупроводниковой промышленности. Частично причиной, по которой производству модулей памяти NAND пришлось перейти на технологию монтажа 3D, были трудности масштабирования. Представьте себе память в виде большого трехмерного небоскреба, каждый из этажей которого соединен «лифтом» – такие «лифты» называются «TSV» или «сквозные каналы» (Through Silicon Vias).

Именно так выглядит будущее, и даже возможно, что скоро чипы GPU/CPU будут монтироваться друг на друга, или память будет монтироваться на CPU. Технология монтажа 3D набирает популярность и в ближайшие 5 лет будет применяться при производстве полупроводников всё чаще и чаще.

Обзор

вариантов реализации монтажа по технологиям 2,5D и 3D

Вместо того чтобы углубляться в детали монтажа по технологиям 3D и 2,5D лучше рассказать о процессах, которые используются в данных технологиях. Я хочу сосредоточиться на процессах, используемых фабриками, которые являются движущей силой развития технологий монтажа 3D и 2,5D.

Обзор

вариантов реализации монтажа по технологиям 2,5D и 3D

Вместо того чтобы углубляться в детали монтажа по технологиям 3D и 2,5D лучше рассказать о процессах, которые используются в данных технологиях. Я хочу сосредоточиться на процессах, используемых фабриками, которые являются движущей силой развития технологий монтажа 3D и 2,5D.

CoWoS от TSMC

Пионером в применении данного процесса стала компания Xilinx, а сам процесс давно стал рабочей лошадкой при производстве полупроводниковой продукции.

В основе процесса лежит размещение логических матриц на кремниевой

подложке, после чего происходит корпусирование сборки. При этом соединение

логических элементов осуществляется за счет сквозных отверстий в кремниевой

пластине или шариковых массивов – иными словами процесс CoWoS от TSMC представляет

собой монтаж по классической технологии 2,5D.

TSMC

SoIC

Вариант реализации монтажа SoIC от компании TSMC является относительно новым.

TSMC

SoIC

Вариант реализации монтажа SoIC от компании TSMC является относительно новым.

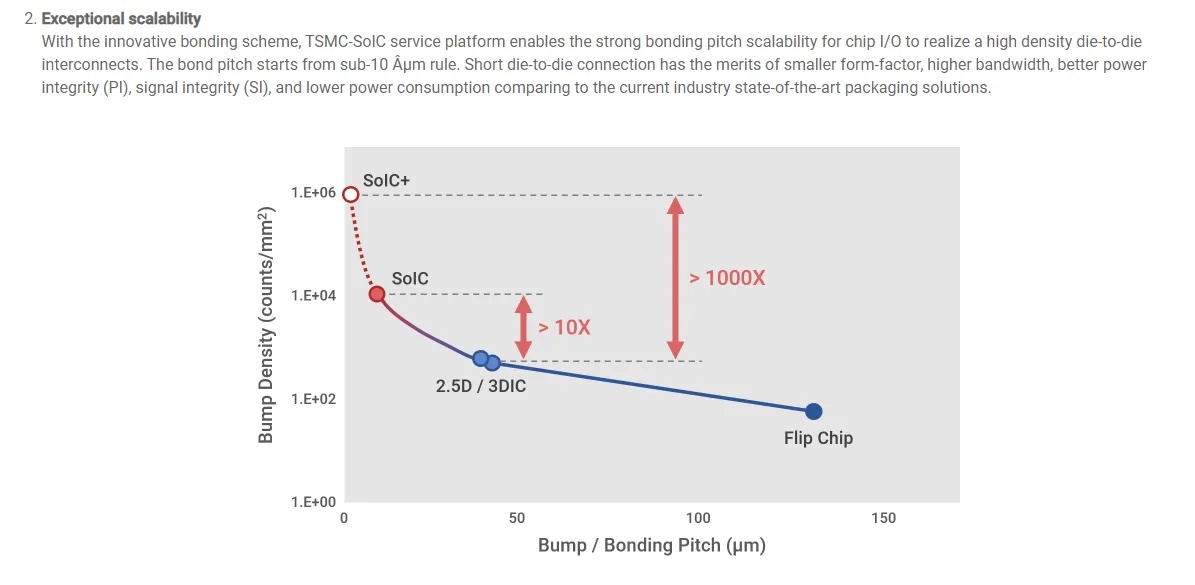

Обратите внимание на график плотности креплений и шага монтажа элементов – SoIC даже близко не стоит с flip chip или 2,5D по размеру и является передовым процессом с точки зрения плотности и размера элементов.

Обратите

внимание, что SoIC использует принципы

монтажа 3D, а не 2,5D.

Samsung

XCube

В последние годы компания Samsung заняла заметное место в производстве полупроводников по технологии 3D и даже разработала свой вариант реализации технологии – Samsung XCube (см. ролик ниже).

В этом месте хочется подчеркнуть, что A100 был изготовлен по техпроцессу Samsung, так что, скорее всего, именно эта технология используется в недавнем чипе Nvidia. Кроме того, из всех компаний, перечисленных в статье, Samsung, вероятно, имеет наибольший опыт работы с TSV благодаря своим модулям памяти, поэтому очевидно компания Samsung хорошо знает своё дело.

Intel

Foevreos

Последним, но не менее важным видом реализации технологии монтажа 3D, является Foveros от компании Intel. Скорее всего, мы увидим больше реализаций от Intel в их «гибридном процессоре» в будущем 7-нм и последующих поколениях. На днях на выставке Architecture days они довольно ясно дали понять, что в своих новых разработках будут фокусироваться именно на этих технологиях.

Интересно то, что в процессах Samsung, TSMC и Intel нет особой разницы.

Победители

революции технологий монтажа

Если вы помните предыдущий пост, который был введением в серию статей о полупроводниках, то технологии монтажа относятся к «промежуточному уровню» (mid-end).

В

прошлом оценки технологий монтажа постоянно исключались из оценок Wafer Fab Equipment (WFE), но с 2020 года отчеты содержат оценку

монтажа на уровне пластин (wafer-level

packaging). Это своего рода сигнал, и поэтому «промежуточный уровень» очень

интересен с этой точки зрения. Другое определение для «промежуточного уровня» – Back End of Line (BOEL).

Подробный разбор компаний, специализирующихся на «промежуточном уровне»

приведен в посте «Packaging Stocks Follow-up».

Перевод статьи Semicap Primer: Packaging History and Primer

Тэги: Технологии

28.07.2023

Перевод статьи Semicap Primer: Packaging History and Primer

Тэги: Технологии

28.07.2023

Nvidia наносит удар по сетям 5G - Ericsson и Nokia ждут трудные времена

Они угробили Intel

Обзор полупроводниковой промышленности на 2026 год

Уроки истории. Великое строительство железных дорог

Уроки истории: Производство полупроводников в 1990-е

Уроки истории. Производство полупроводников в 1980-х

Уроки истории. Крах телекома

Semicap. Обзор технологий высокоплотного монтажа

Оборудование для производства полупроводников. Введение

Почему Советский Союз так и не добрался до Луны?

Nokia 2.0

Американские сенаторы предлагают налоговые льготы для производитей полупроводников

Безос, Брэнсон, Маск: что нужно знать о новой космической гонке

Годовой обзор беспроводных сетей в США – важные моменты

Как беспилотники за 44 дня поставили точку в затянувшемся конфликте

Опубликованы документы о связях компании Huawei c программами незаконной слежки за гражданами

Как китайские хакеры американцев ломали

Операция ЦРУ по получению данных о советских ракетах

Google. Когда не мышь находится в лабиринте, а лабиринт в мыши

Alexander (c) Stikhin